# **COMPUTER SYSTEM ARCHITECTURE**

# **CONTENTS**

**UNIT-1: Digital Components**

**UNIT-2: Input-Output Organization**

**UNIT-3: Memory Unit**

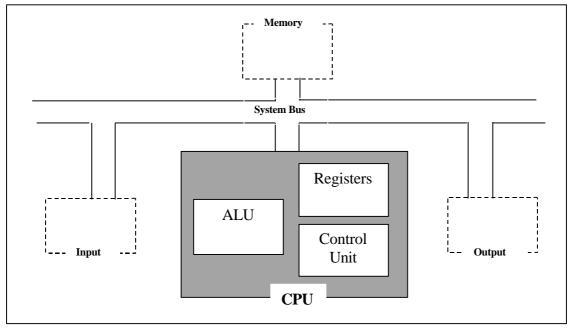

**UNIT- 4 : CPU Organization**

**UNIT-5: Multi-Processor Organization**

**UNIT-6: Pipelining**

# **UNIT STRUCTURE**

- 1.1 Learning Objectives

- 1.2 Introduction

- 1.3 Combinational Circuits

- 1.3.1 Half-Adder

- 1.3.2 Full-Adder

- 1.3.3 Half-Subtractor

- 1.3.4 Full-Subtractor

- 1.3.5 Multiplexer

- 1.3.6 Demultiplexer

- 1.3.7 Encoder

- 1.3.8 Decoder

- 1.3.9 Magnitude Comparator

- 1.4 Sequential Circuits

- 1.5 Flip-Flops

- 1.5.1 RS Flip-Flop

- 1.5.2 D Flip-Flop

- 1.5.3 JK Flip-Flop

- 1.5.4 MS Flip-Flop

- 1.6 Counters

- 1.6.1 Asynchronous Counter

- 1.6.2 Synchronous Counter

- 1.7 Register

- 1.7.1 Serial In Serial Out Register

- 1.7.2 Serial In Parallel Out Register

- 1.7.3 Parallel In- Serial Out Register

- 1.7.4 Parallel In- Parallel Out Register

- 1.8 Let Us Sum Up

- 1.9 Answers To Check Your Progress

- 1.10 Further Readings

- 1.11 Model Questions

# 1.1 LEARNING OBJECTIVES

After going through this unit, you will be able to:

- define combinational circuit

- define sequential circuit

- describe working principle of half-adder and full-adder

- describe the working principle of half-subtractor and full-subtractor

- describe the working principle of multiplexer and demultiplexure

- describe the working principle of encoder and decoder

- describe the working principle of flip-flop

- describe the working principle of register

- describe the working principle of counter

## 1.2 INTRODUCTION

You have already been acquainted with different combinational and sequential circuits in *Unit-4* of *BCA(F1)01*. Before going ahead, you may read that unit and start learning this unit with ease.

Various combinational and sequential circuits are discussed here to build your understanding on different digital components that are used in digital applications. A sound knowledge on these components will make you feel confident to understand the working principle of many digital devices in general and the computer system in particular.

## 1.3 COMBINATIONAL CIRCUITS

A circuit is called a combinational circuit when its output is solely determined by its present input.

Inputs can take values either 0 or 1 and outputs are also available as either 0 or 1. Since the output is related to the inputs by a Boolean expression, therefore a truth table is always associated with all combinational circuits. Conversely, a Boolean expression can be obtained for a combinational circuit from the truth table.

# 1.4 HALF-ADDER

Half-adder is a circuit that can add two binary bits. Its outputs are SUM and CARRY. The following truth table shows various combinations of inputs and their corresponding outputs of a half-adder. X and Y denote inputs and C and S denote CARRY and SUM.

| Х | Υ | CARRY(C) | SUM (S)              |

|---|---|----------|----------------------|

| 0 | 0 | 0        | 0                    |

| 0 | 1 | 0        | 1( X Y)              |

| 1 | 0 | 0        | $1 (X \overline{Y})$ |

| 1 | 1 | 1(XY)    | 0                    |

Truth Table for a Half-Adder

The minterms for SUM and CARRY are shown in the bracket. The Sum-Of-Product (SOP) equation for SUM is:

Similarly, the SOP equation for the CARRY is:

$$C = XY \qquad \dots (2)$$

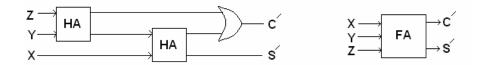

Combining the logic circuits for equation (1) & (2) we get the circuit for Half-Adder as:

Fig 1.1 : Half-Adder Circuit and Symbol

## 1.5 FULL-ADDER

Full-Adder is a logic circuit to add three binary bits. Its outputs are SUM and CARRY. In the following truth table X, Y, Z are inputs and C and S are CARRY and SUM.

| Х | Υ | Z | CARRY(C) | SUM (S) |

|---|---|---|----------|---------|

|   |   |   |          |         |

| 0 | 0 | 0 | 0        | 0       |

| 0 | 0 | 1 | 0        | 1       |

| 0 | 1 | 0 | 0        | 1       |

| 0 | 1 | 1 | 1        | 0       |

| 1 | 0 | 0 | 0        | 1       |

| 1 | 0 | 1 | 1        | 0       |

| 1 | 1 | 0 | 1        | 0       |

|   |   |   | 1(XYZ)   | 1(XYZ)  |

Truth Table for a Full-Adder

The minterms are written in the brackets for each 1 output in the truth table. From these the SOP equation for SUM can be written as:

( Exclusive OR and equivalence functions are complement to each other). Here S is SUM of Half-Adder.

Again, SOP equation for Full-Adder CARRY is :

$$C = \overline{X}YZ + X\overline{Y}Z + XY\overline{Z} + XYZ$$

$$= \overline{X}YZ + XYZ + X\overline{Y}Z + XY\overline{Z}$$

$$= \overline{\Theta} + X \overline{Y}Z + X \overline{\Theta} Z + Y\overline{Z} \overline{J}$$

$$= YZ + XS$$

$$= C + XS \dots (4)$$

Here also C means CARRY of half-adder and S means SUM of half-adder.

Now using two half-adder circuits and one OR gate we can implement equation (3) and (4) to obtain a full-adder circuit as follows:

Fig 1.2 : Full-Adder Circuit and its Symbol

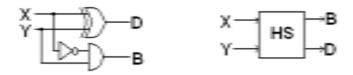

## 1.3.3 HALF-SUBTRACTOR

A half-subtractor subtracts one bit from another bit. It has two outputs viz DIFFERENCE (D) and BORROW (B).

| Х | Υ | BORROW (B)             | DIFFERENCE (D)         |

|---|---|------------------------|------------------------|

| 0 | 0 | 0                      | 0                      |

| 0 | 1 | 1 <b>€</b> ₹Y <b>j</b> | 1 <b>⊛</b> ¯Y <b>j</b> |

| 1 | 0 | 0                      | 1 <b>⊜</b> :₹ <b>j</b> |

| 1 | 1 | 0                      | 0                      |

Truth Table for Half-Subtractor

The mean terms are written within parenthesis for output 1 in each column. The SOP equations are :

$$D = \overline{X} Y + X \overline{Y}$$

$$= X \oplus Y \dots (5)$$

Fig 1.3: The half-subtractor circuit and the symbol

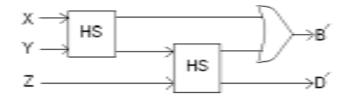

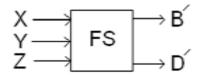

## 1.3.4 FULL-SUBTRACTOR

A full-subtractor circuit can find Difference and Borrow

arising on the subtraction operation involving three binary bits.

| Х | Υ | Z | BORROW (B')                                        | DIFFERENCE (D')                 |

|---|---|---|----------------------------------------------------|---------------------------------|

| 0 | 0 | 0 | 0                                                  | 0                               |

| 0 | 0 | 1 | 1 <b>0</b> YZ                                      | 1 <b>₫</b> ₹Z                   |

| 0 | 1 | 0 | 1 <b>€</b> YZ                                      | 1 <b>€</b> ₹ŸŹ <b>j</b>         |

| 0 | 1 | 1 | 1 <b>€</b> ₹YZ <b>j</b><br>1 <b>€</b> ₹YZ <b>j</b> | 0                               |

| 1 | 0 | 0 | 0                                                  | 1 <b>G</b> \overline{\text{YZ}} |

| 1 | 0 | 1 | 0                                                  | 0                               |

| 1 | 1 | 0 | 0                                                  | 0                               |

| 1 | 1 | 1 | 1(XYZ)                                             | 1(XYZ)                          |

Truth Table for Full-Subtractor

The SOP equation for the DIFFERENCE IS:

$$D' = \overline{X}\overline{Y}Z + \overline{X}Y\overline{Z} + X\overline{Y}\overline{Z} + XYZ$$

$$= \overline{X}Y\overline{Z} + X\overline{Y}\overline{Z} + XYZ + \overline{X}\overline{Y}Z$$

$$= \overline{Q}Y + X\overline{Y}\overline{Z} + \overline{Q}XY + \overline{X}\overline{Y}\overline{Z}$$

$$= D\overline{Z} + \overline{D}Z \qquad (7)$$

And SOP equation for BORROW is:

$$B' = \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ}$$

$$= \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ}$$

$$= \overline{QY} + \overline{XY}Z + \overline{XY}Q + \overline{Z}I$$

$$= D\overline{Z} + \overline{XZ} \qquad (7)$$

In equation (7) and (8), D stands for DIFFERENCE output of half-subtractor. Now, from the equations (7) and (8) we can construct a full-subtractor using two half-subtractor and an OR gate.

Fig. 1.4: Full-Subtractor circuit

#### CHECK YOUR PROGRESS

Choose the correct answer:

- 1. A half-adder can add

- (a) Two binary numbers (b) Two binary bits of 4 bits each

- (c) Add half of a binary (d) None of these number

- 2. A full-adder is a logic circuit that has two outputs namely:

- (a) product & Sum

- (b) sum & borrow

- (c) sum & carry

- (d) carry & borrow

- 3. A half-subtractor can perform

- (a) subtraction of two binary bits

- (b) product of two binary bits

- (c) complement of half

- (d) none of these

binary bits

- 4. A full-subtractor has the ability to do

- (a) subtraction of two binary numbers

- (b) subtraction of three binary bits

- (c) product of three binary bits

- (d) division three binary bits

#### 1.3.5 MULTIPLEXER

Multiplexer is a circuit which has many inputs and only one output. Multiplexer can select any one of its many inputs by using selection lines and steer the selected input to the output. Generalized block diagram of a multiplexer is shown in Fig. 1.5.

Fig. 1.5 : Block Diagram of Multiplexer

It has  $2^n$  inputs, n – numbers of selection lines and only one output. A multiplexer is also called a many – to – one data selector.

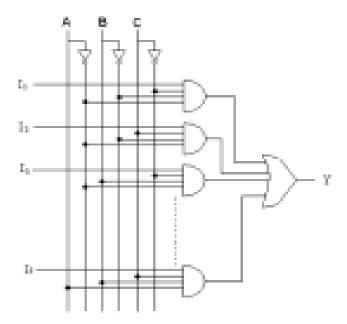

#### 8 - to - 1 MULTIPLEXER:

Fig 1.6 shows a 8-to-1 multiplexer, where there are 8 inputs, 3 selection lines and 1 output. The eight inputs are labeled as  $I_0, I_1, I_2, I_3, I_4, I_5, I_6, I_7$  and the selection lines are as A, B, C. Which input is steered to the output depends on the value of ABC. As for example, if

$$ABC = 000$$

then the upper AND gate is enabled and all other AND gates are disabled. As a result, the input  $I_0$  alone is steered to the output. Similarly, if

$$ABC = 110$$

Then the AND gate connected to the data line  $I_6$  is enabled while all the other AND gates are disabled. Therefore, the input  $I_6$  appears at the output. Hence when ABC = 110, the output is Y =  $I_6$

Fig. 1.6: 8-to-1 Multiplexer

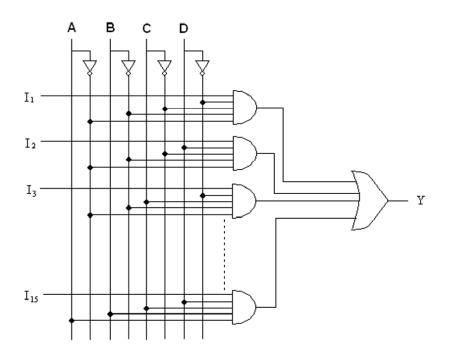

#### 16 - to -1 MULTIPLEXER :

Fig 1.7 shows a 16 – to – 1 multiplexer. In this circuit, there are 16 data input lines, 4 selection lines and 1 output. The input lines are denoted by  $I_0, I_1, I_2, I_3, \dots _{15}$  and the selection lines are by ABCD. The output is denoted by Y.

Out of 16 input lines, only one is transmitted to the output depending upon the value of ABCD. If

$$ABCD = 0000$$

then  $I_0$  is steered to the output since the upper AND gate is enabled alone and all others are disabled. Similarly, if

$$ABCD = 0010$$

then  $I_2$  appears at the output. If

$$ABCD = 1111$$

the the last AND gate is one enabled and therefore,  $I_{15}$  appears at the output.

Fig. 1.7 16-to-1 Multiplexer

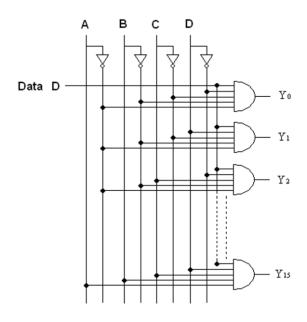

## 1.3.6 DE-MULTIPLEXER

It is opposite to the multiplexer. De-multiplexer has 1 input and many outputs. With the application of appropriate control signal, the common input data can be steered to one of the output lines. Fig 1.8 shows a generalized block diagram of a de-multiplexer.

Fig. 1.8: Block diagram of a De-Multiplexer

To have 2<sup>n</sup> output lines, there must be n control lines in a de-multiplexer.

**1-to-16 DE- MULTIPLEXER**: In Fig 1.9 we have shown a 1-to-16 de-multiplexer.

Fig 1.9: 1-to-16 De-Multiplexer

Here, the data input line is denoted by D. This input line is connected to all the AND gates through which output appears. Depending upon the control signal, only one AND gate becomes enabled and the data input D appears through that AND gate. So, when ABCD = 0000, the upper AND gate is enabled and data input D appears at  $Y_0$  as output.

When ABCD = 1111, the bottom AND gate becomes enabled and D appears at  $Y_{15}$  as output. For other combination, D appears at other output terminal.

## **CHECK YOUR PROGRESS**

Give the correct answer:

- 5. Multiplexer means

- (a) multiple to many

- (b) one to many

- (c) many to one

- (d) one to one

- 6. A 16-to-1 multiplexer has

- (a) 1 selection lines

- (b) 2 selection lines

- (c) 3 selection lines

- (d) 4 selection lines

- 7. De-multiplexer means

- (a) deduct multiple bits

- (b) one-to-many

- (c) multiple-to-multiple

- (d) one-to-one

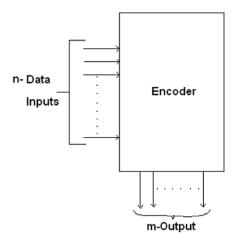

#### 1.3.7 ENCODER

An encoder converts a digital signal into a coded signal.

A generalized view of an encoder is shown in Fig 1.10.

Fig. 1.10: Block diagram of an Encoder

In the figure, we can see that there are n input lines and m numbers of output lines where  $n \leq 2^m$ . Out of n inputs, only one input line is active at a time. Encoder generates a coded output which is unique for each of the active input.

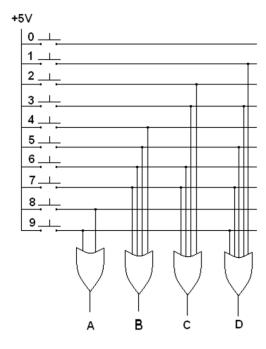

## DECIMAL- TO -BCD ENCODER :

Fig. 1.11: Decimal-to-BCD Encoder

A decimal to BCD encoder is shown in Fig 1.11 This circuit generates BCD output when any one of the push button switches is pressed. As for example, if button 6 is pressed, the B and C OR gates have high inputs and the corresponding output becomes

$$ABCD = 0110$$

If button 8 is pressed, the OR gate A receives a high input and therefore the output becomes

$$ABCD = 1000$$

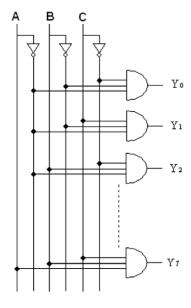

## 1.3.8 DECODER

A decoder is a digital circuit which has n-input lines and 2<sup>n</sup> output lines. A decoder and a de-multiplexer has similarity. In a de-multiplexer, there is a single input line connected to every output 'AND' gate whereas in a decoder that input line is absent.

Let us draw a 3 - to - 8 decoder as shown in Fig 1.12. Its truth table is shown below:

| lı | Inputs |   |                |                | (              | Output         | S     |                |                |                |

|----|--------|---|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| А  | В      | О | Y <sub>0</sub> | Y <sub>1</sub> | Y <sub>2</sub> | Y <sub>3</sub> | $Y_4$ | Y <sub>5</sub> | Y <sub>6</sub> | Y <sub>7</sub> |

| 0  | 0      | 0 | 1              | 0              | 0              | 0              | 0     | 0              | 0              | 0              |

| 0  | 0      | 1 | 0              | 1              | 0              | 0              | 0     | 0              | 0              | 0              |

| 0  | 1      | 0 | 0              | 0              | 1              | 0              | 0     | 0              | 0              | 0              |

| 0  | 1      | 1 | 0              | 0              | 0              | 1              | 0     | 0              | 0              | 0              |

| 1  | 0      | 0 | 0              | 0              | 0              | 0              | 1     | 0              | 0              | 0              |

| 1  | 0      | 1 | 0              | 0              | 0              | 0              | 0     | 1              | 0              | 0              |

| 1  | 1      | 0 | 0              | 0              | 0              | 0              | 0     | 0              | 1              | 0              |

| 1  | 1      | 1 | 0              | 0              | 0              | 0              | 0     | 0              | 0              | 1              |

Truth table for a 3-to-8 decoder

Fig. 1.12 : 3-to-8 decoder

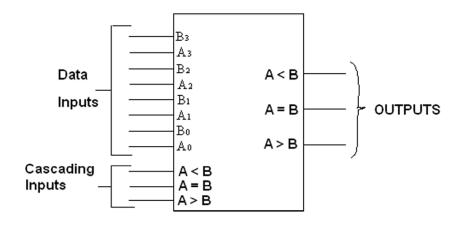

## 1.3.9 MAGNITUDE COMPARATOR

A magnitude comparator circuit can compare two binary numbers to determine which one is greater than the other or their equality. Such a magnitude comparator has three output lines for A > B, A = B, A < B where A & B are two n-bits binary numbers. Every bit of one number is compared with the corresponding bit of the other number by ExOR gate.

A 4-bit magnitude comparator, SN 7485 is available in chip form the block diagram of which is shown in Fig 1.13. It compares two 4-bit binary numbers  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$ . Three output terminals are available for A < B, A = B and A > B

Fig. 1.13: Two 4-bit words magnitude comparator SN 7485

#### **FUNCTION TABLE SN 7485**

|                                           | Compa                               | ring Inpu                                 | uts                                 | Cas         | cading I    | nputs  |             | Outputs     |             |

|-------------------------------------------|-------------------------------------|-------------------------------------------|-------------------------------------|-------------|-------------|--------|-------------|-------------|-------------|

| $A_3B_3$                                  | $A_2B_2$                            | $A_1B_1$                                  | $A_0B_0$                            | A > B       | A < B       | A = B  | A > B       | A < B       | A = B       |

| $A_3 > B_3$                               | X                                   | X                                         | X                                   | Х           | - X         | X      | Н           | L           | L           |

| $A_3 < B_3$                               | X                                   | X                                         | X                                   | X           | X           | X      | L           | Н           | L           |

| $A_3 = B_3$                               | $A_2 > B_2$                         | X                                         | X                                   | Х           | X           | X      | Н           | L           | L           |

| $A_3 = B_3$                               | $A_2 < B_2$                         | X                                         | X                                   | , <b>X</b>  | X           | X      | L           | Н           | L           |

| $A_3 = B_3$                               | $A_2 = B_2$                         | $A_1 > B_1$                               | X                                   | Х           | X           | X      | Н           | L           | L           |

| $A_3 = B_3$                               | $A_2 = B_2$                         | $A_1 < B_1$                               | Х                                   | Х           | Х           | X      | L,          | Н           | L           |

| $A_3 = B_3$                               | $A_2 = B_2$                         | $A_1 = B_1$                               | $A_0 > B_0$                         | Х           | X           | X      | Н           | L           | L           |

| $A_3 = B_3$                               | $A_2 = B_2$                         | $A_1 = B_1$                               | $A_0 < B_0$                         | X           | X           | X      | L           | Н           | L.          |

| $A_3 = B_3$<br>$A_3 = B_3$<br>$A_3 = B_3$ | $A_2 = B_2$ $A_2 = B_2$ $A_2 = B_2$ | $A_1 = B_1$<br>$A_1 = B_1$<br>$A_1 = B_1$ | $A_0 = B_0$ $A_0 = B_0$ $A_0 = B_0$ | H<br>L<br>L | L<br>H<br>L | L<br>H | H<br>L<br>L | L<br>H<br>L | L<br>H<br>` |

To compare any number having more than 4-bits, two or more such chip can be cascaded. The A > B, A < B and A = B outputs of a stage that handles less significant bits are connected to the corresponding cascading inputs of the next stage that handles the more significant bits.

## **CHECK YOUR PROGRESS**

Give the correct answer:

- 8. An encoder

- (a) converts a digital input to another form of digital output.

- (b) converts analog input to digital output

- (c) selects one out of many inputs.

- (d) none of these.

- 9. Decoder has n inputs line and

- (a) n output lines.

- (b) 2<sup>n</sup> output lines.

- (c) n<sup>2</sup> output lines.

- (d) no output lines.

- 10. Magnitude comparator

- (a) compares two multi bit binary number.

- (b) magnify any digital signal.

- (c) compress binary numbers.

- (d) check error in a binary number.

## 1.4 SEQUENTIAL CIRCUITS

If the output of a circuit depends on its present inputs and immediate past output, then the circuit is called sequential circuit. To build a sequential circuit, we need memory circuits and combinational circuits. Flip-Flop is used as memory circuit the application of which we would see in counter, register etc.

## 1.5 FLIP- FLOPS

A digital circuit that can produce two states of output, either high or low, is called a multivibrator. Three types of multivibrators are-monostable, bi-stable and a stable.

A Flip-Flop is a bi-stable multivibrator and therefore it has two stable states of output-either high or low. Depending on its outputs and previous inputs, its new output is either high (or 1) or low (or 0). Once the output is fixed, the inputs can be removed and then also the already fixed output will be retained by the flip-flop. Hence a flip-flop can be used as basic circuit of memory for storing one bit of data. To store multiple bits we can use multiple numbers of flip-flop. Flip-flops are also used to build counter, register etc.

There are many types of flip-flops. These are:

- RS Flip-flop

- D Flip-Flop

- JK Flip-Flop

- MS Flip-Flop

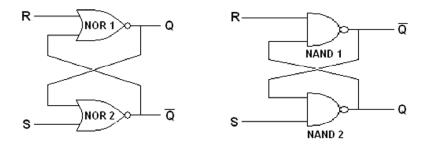

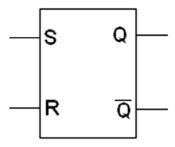

## 1.5.1 RS FLIP-FLOP

RS flip-flop is also called Set-Reset flip-flop. An RS flip-flop can be built using a pair of NOR gates or NAND gates. Here we have shown two RS flip-flop circuits using NOR and NAND gate. To study its working principle, we can use any one of them. In the following section, let us consider the RS flip-flop using NOR gate.

Fig. 1.14 : Basic circuit of RS flip-flop using NOR and NAND gate.

RS flip-flop has two inputs: Set (S) and Reset(R). It has two outputs, Q and  $\overline{Q}$ . It should be noted  $\overline{Q}$  is always the complement of Q. Various combinations of inputs and their corresponding outputs are listed in the truth table below :

| R | S | Q          | Action    |

|---|---|------------|-----------|

| 0 | 0 | Last value | No change |

| 0 | 1 | 1          | Set       |

| 1 | 0 | 0          | Reset     |

| 1 | 1 | ?          | Forbidden |

|   |   |            |           |

Truth table of RS flip-flop

The first input condition in the table is R=0, S=0. Since a

0 input has no effect on its output, the Flip-Flop retains its previous state. Hence Q remains unchanged.

The second input condition R=0, S=1 forces the output of NOR gate2 low. This low output will reach NOR gate1 and when both inputs of NOR gates1 is low, its inputs Q will be high. Thus, a 1 at the S input will SET the flip-flop and Q will be equal to 1.

The third input condition R=1, S=0 will force the output of NOR gate1 to low. This low will reach NOR gate2 and forces its outputs to high. Hence, when R=1, S=0, then Q=0,  $\overline{Q}$ =1. Thus, the flip-flop is RESET.

The last input condition in the table R=1, S=1 is forbidden since it forces both the NOR gates to the low state, means both Q=0, and  $\overline{Q}$ =0 at the same time, which violets the basic definition of flip-flop that requires Q to be the complement of  $\overline{Q}$ . Hence, this input condition is forbidden and its output is unpredictable.

Fig. 1.15 : Symbol of RS Flip-Flop

#### **CLOCK INPUT:**

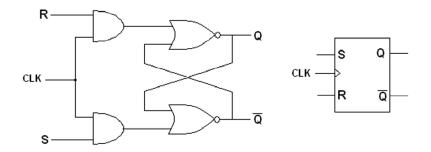

For synchronization of operation of multiple flip-flop, an additional signal is added to all types of flip-flop which is called clock signal, generally abbreviated as CLK. Addition of CLK signal ensures that, whatever may be the input to the flip-flop, it effects the output only when CLK signal is given. Fig. 1.16 shows a clocked RS flip-flop.

Fig. 1.16 : Clocked RS flip-flop Symbol of Clock RS flip-flop

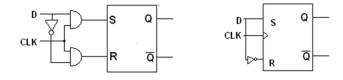

#### 1.5.2 D FLIP-FLOP

D flip-flop is a modification of RS flip-flop. In RS flip-flop when both the inputs are high i.e., R=1, S=1, the output becomes unpredictable and this input combination is termed as forbidden. To avoid this situation, the RS flip-flop is modified so that both the inputs can not be same at a time. The modified flip-flop is called D flip-flop. Fig 1.17 shows a clocked D flip-flop.

Fig. 1.17: (a) Clocked D flip-flop Symbol of D flip-flop

In D flip-flop both inputs of RS flip-flop are combined together to make it one by a NOT gate so that inputs can not be same at a time. Hence in D flip-flop there is only one input. The truth table is:

| CLK | D | Q          |

|-----|---|------------|

| 0   | Х | Last state |

| 0   | 0 | 0          |

| 1   | 1 | 1          |

In a clocked D flip-flop the value of D cannot reach the output Q when the clock pulse is low. During a low clock, both AND

gates are disabled. Therefore, D can change value without affecting the value of Q. On the other hand, when the clock is high, both AND gates are enabled. In this situation, Q is forced to be equal to the value of D. In another way we can say that in the D flip-flop above, Q follows the value of D while the clock is high. This kind of D flip-flop is often called a D latch.

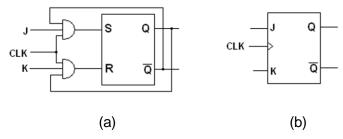

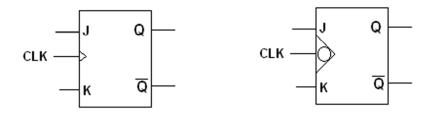

## 1.5.3 JK FLIP-FLOP

In RS flip-flop, the input R= S=1 is called forbidden as it causes an unpredictable output. In JK flip-flop this condition is used by changing the RS flip-flop in some way. In JK flip-flop both input can be high simultaneously and the corresponding toggle output makes the JK flip-flop a good choice to build counter- a circuit that counts the number of +ve or -ve clock edges. Fig 1.18 shows one way to build a JK flip-flop.

Fig. 1.18 : (a) JK Flip-Flop (b) Symbol of JK Flip-Flop

| CLK      | J | K | Q          |

|----------|---|---|------------|

| Х        | 0 | 0 | Last state |

| <b>↑</b> | 0 | 1 | 0          |

| <b>↑</b> | 1 | 0 | 1          |

| <b>↑</b> | 1 | 1 | Toggle     |

Truth table for JK flip-flop

The inputs J and K are called control inputs because their combinations decide what the output of JK flip-flop will be when a +ve clock pulse arrives. When J and K are both low, both the

AND gates are disabled. Therefore, the CLK pulse has no effect. The first input combination of the truth table shows this and under this case the output Q retains its last state.

When J is low, K is high, the upper AND gate is disabled while the lower AND gate is enabled. Hence the flip-flop cannot be set; instead it is reset, i.e. Q=0. This is shown by the second entry in the truth table.

When J is high, K is low the upper AND gate is enabled while the lower one is disabled. So the flip-flop is set there by making Q = 1.

When J and K are both high, then the flip-flop is set or reset depending on the previous value of Q. If Q is high previously, the lower AND gate sends a RESET trigger to the flip-flop on the next clock pulse. Then Q becomes equal to 0. On the other hand, if Q is low previously, the upper AND gate sends a SET trigger on the flip-flop making Q=1.

So, when J = K = 1, Q changes its value from 0 to 1 or 1 to 0 on the positive clock pulse. This changing of Q to  $\overline{Q}$  is called toggle. Toggle means to change to the opposite state.

Any flip-flop may be driven by +ve as well as -ve clock. As such JK flip-flop can also be driven by positive clock as well as negative clock. Fig 1.19 shows symbol of positive clocked and negative clocked JK flip-flop.

Fig. 1.19 : Positive clocked JK

Flip-Flop

Flip-Flop

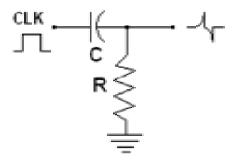

#### **RC** Differentiator Circuit:

The clock pulse applied to a flip-flop is a square wave signal. Clock pulse is used to achieve synchronization of flip-flop operation. To make the synchronization more precise, the square wave pulse is further modified to make it a narrow spike by using a RC differentiator circuit as shown in fig 1.20

Fig. 1.20: RC Differentiator Circuit

The upper tip of the differentiated pulse is called positive edge and the lower tip is called is negative edge. When a flip-flop is triggered by this type of narrow spike, it is called edge triggered flip-flop. If the flip-flop is driven by +ve edge, it is called +ve edge triggered flip-flop. If it is a driven by negative edge, it is called negative edge triggered flip-flop.

#### Racing

In a flip-flop if the output toggles more than once during a clock pulse then it is called *racing*. All flip-flop has a propagation delay which means the output changes its state after a certain time period from applying the input and the clock pulse. So, when a flip-flop is edge triggered, then due to propagation delay the output cannot affect the input again, because by that time the edge of clock pulse has already passed away. If the propagation delay of a flip-flop in 20 ns and the width of the spike is less than 20 ns, than the returning Q and  $\overline{Q}$  arrive too late to cause false triggering.

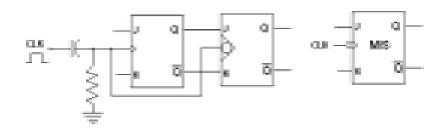

## 1.5.4 MS FLIP-FLOP

MS flip-flop is another way to avoid racing. Fig 1.21 shows one way to build MS flip-flop using two JK flip-flop, one of which is positive edge triggered and the other is negative edge triggered. The first JK flip-flop is master and the latter is slave. The master responds to its J and K inputs at the positive edge. J=1, K=0, the master sets on the positive clock edge. The high Q output of the master drives the J input of the slave. So, at the negative clock edge, the slave also sets, copying the action of the master.

When J=0, K=1, master resets at +ve clock edge and the slave resets of the -ve clock edge.

When J = K = 1 master toggles at +ve clock edge, and the slave toggles at the -ve clock edge.

Hence, whatever master does, the slave copies it.

MS flip-flop is a very popular flip-flop in industry due to its inherent resistance to racing. Hence, to build counter it is extensively used.

Fig.1.21:

- (a) Edge triggered JK MS flip-flop

- (b) Symbol of JK MS flip-flop

## **CHECK YOUR PROGRESS 4**

- 11. A flip-flop is basically a

- (a) mono-stable multi-vibrator

- (b) a stable multi-vibrator

- (c) bi-stable multi-vibrator

- (d) none of these.

- 12. JK flip-flop has the specialty in

- (a) fast response time

- (b) toggle property

- (c) spike shaped clock input

- (d) preset input

- 13. In MS flip-flop the master changes state

- (a) after the slave

- (b) with the slave at the same time

- (c) before the slave

- (d) never

## 1.6 COUNTER

A counter is one of the most useful sequential circuits in a digital system. A counter driven by a clock can be used to count the number of clock cycles. Since the clock pulse has a definite time period, the counter can be used to measure time, the time period or frequency.

There are basically two types of counter: **Synchronous counter** and **asynchronous counter**.

Counters are constructed by using flip-flops and other logic gates. If the flip-flops are connected serially then the output of one flip-flop is applied as input to the next flip-flop. Therefore, this type of counter has a cumulative settings time due to propagation delay. Counters of this type are called serial or asynchronous counter. These counters have speed limitation.

Speed can be increased by using parallel or synchronous counter.

Here, flip-flops are triggered by a clock at a time and thus setting time is equal to the propagation delay of a single flip-flop. But this type of synchronous counters require more hardware and hence they are costly.

Combination of serial or parallel counter is also done to get an optimum solution of speed and hardware/cost. If each clock pulse advances the contents of the counter by one, it is called *up counter*. If the content of the counter goes down at each clock pulse, it is called *down counter*.

Before operation, some time it is required to reset all the flip-flops to zero. It is called "Clear". Some time, it is required to set the flip-flops. It is called *preset*. To do these, two extra inputs are there in every flip-flop called CLR and PR.

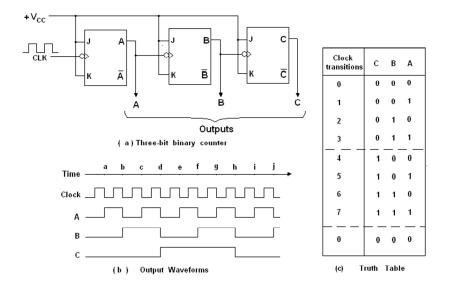

## 1.6.1 Asynchronous Counter

When the output of a flip-flop is used as the clock input for the next flip-flop it is called asynchronous counter.

Asynchronous counters are also called ripple counter because flip-flop transitions ripple through from one flip-flop to the next in a sequence until all flip-flops reach a new state.

A binary ripple counter can be constructed by using clocked JK flip-flop. Fig 1.22(a) shows three MS JK flip-flops connected in series. The clock drives flip-flop A. The output of A drives B and the output of B drives C. J and K inputs of all the flip-flops are connected to positive to make them equal to 1. Under this condition each flip-flop will change state (toggle) with a negative transition at its clock point.

In the counter shown in Fig 1.22 (a), the flip-flop A changes its state at the negative edges of the clock pulses. Its output is applied to the B flip-flop as its clock input.

Fig. 1.22: Three Bit Binary Counter

The output of B flip-flop toggles at the negative edges of the output of A flip-flop. Similarly, the output of B flip-flop is used as clock input of the C flip-flop and therefore C toggles at the negative edges of the output of B flip-flop. We can see that triggering pulses move through the flip-flops like a ripple in water.

The wave form of the ripple counter is shown in fig 1.22(b). It shows the action of the counter as the clock runs. To understand the wave form let us assume that the counter is cleared before the operation. The A output is assumed the list significant bit(LSB) and C is the most-significant-bit (MSB). Hence, at the very beginning the contents of the counter is CBA=000.

Flip-flop A changes its state to 1 after the negative pulse transition. Thus, at point A on the time line, A goes high. At point b it goes low, at C it goes back to high and so on.

Now, output of A acts as clock input of B. So, each time the output of A goes low, flip-flop B will toggle. Thus, at point B on the time line, B goes high at point b and it goes low at point d, and toggles back high again at point f and so on.

Since B acts as the clock input for C, each time the output of B goes low, the C flip-flop toggles. Thus C goes high at point d on the time line, it goes back to low again at point h.

We can see, at the output, wave form of A has half the frequency than the clock input wave. B has half the frequency than that of A and C has half the frequency than that of B.

We can further see that since the counter has 3 flip-flops cascaded together, it progresses through 000---- 001----010--- 011---100---101---111 as its CBA output. After CBA= 111,it starts the cycle again from CBA=000. One cycle from 000---111 takes 8 clock pulses, as it is evident from the wave form as well as from the truth table.

## 1.6.2 Synchronous Counter

An asynchronous counter or ripple counter has limitation in its operating frequency. Each flip-flop has a delay time which is additive in asynchronous counter.

In synchronous counter the delay of asynchronous counter is overcome by the use of simultaneous applications of clock pulse to all the flip-flops. Hence, in synchronous counter, the common clock pulse triggers all the flip-flops simultaneously and therefore the individual delay of flip-flop does not add together. This feature increases the speed of synchronous counter. The clock pulse applied can be counted by the output of the counter.

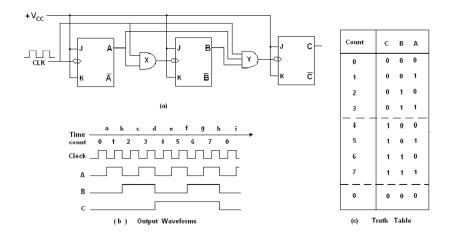

To build a synchronous counter, flip-flops and some additional logic gates are required. Fig 1.23 shows a three stage synchronous or parallel binary counter along with its output wave forms and truth table. Here the J and K inputs of each flip-flop is kept high and therefore the flip-flops toggle at the negative clock transition at its clock input. From figure we can see that the output of A is ANDed with CLK to drive the 2nd flip-flop and the outputs of A, B are ANDed with CLK to drive the third flip-flop. This logic configuration is often referred to as "steering logic" since the clock pulses are steered to each individual flip-flop.

In the figure, the clock pulse is directly applied to the first flip-flop. Its J and K are both high, so the first flip-flop toggles state at the negative transition of the input clock pulses. This can be seen at points a,b,c,d,e,f,g,h,i on the time line.

The AND gate X is enabled when A is high, and it allows a clock pulse to reach the 2nd flip-flop. So the 2nd flip-flop toggles with every other negative clock transition at points b, d, f and h on the time line.

Fig. 1.23: Parallel Binary Counter

The AND gate Y is enabled only when both A and B are high and it transmits the clock pulses to the clock input of the 3rd flip-flop. The 3rd flip-flop toggles state with every fourth negative clock transition at d and h on the time line.

The wave form and the truth table shows that the synchronous counter progresses upward in a natural binary sequence from 000 to 111. The total count from 000 to 111 is 8 and hence this counter can also be called MOD-8 counter, in count up mode.

## **CHECK YOUR PROGRESS**

- 14. State True or False

- (a) Counters are non sequential digital circuits.

- (b) Asynchronous counters are fast in operation than synchronous counters.

- (c) The natural progression of a counter is called MODE.

- (d) Counters can be used to build digital clock.

# 1.7 REGISTER

A number of flip-flops connected to store binary number is called a register. The number to be stored is entered or shifted into the register and also taken out or shifted out as per necessity. Hence, registers are also known as shift register.

Registers are used to store data temporarily. Registers can be used to perform some important arithmetic operations like complementation, multiplication, division etc. It can be connected to form counters, to convert serial data to parallel and parallel to serial data.

Types of registers: According to shifting of binary number also called shift registers, different types of registers are:

- Serial In—Serial Out (SISO)

- Serial In –Parallel Out (SIPO)

- Parallel In –Serial Out (PISO)

- Parallel In –Parallel Out (PIPO)

## 1.7.1 Serial In - Serial Out (SIPO)

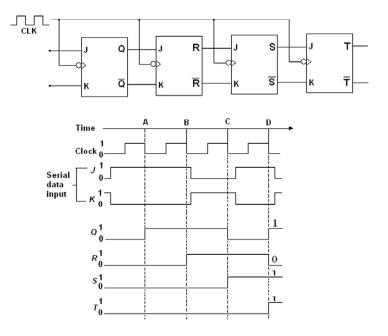

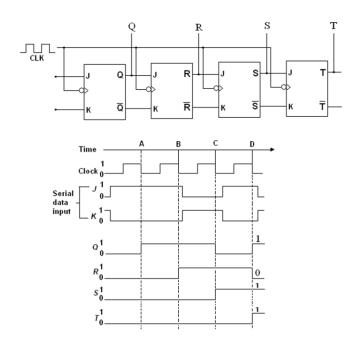

Fig 1.24 shows a typical 4 bit SISO register using flip-flops. Here the content of the register is named as QRST. Let us consider that all flip-flops are initially reset. Hence, at the beginning QRST= 0000. Let us consider a binary number 1011 which we want to store in the SISO register.

At time A: A 1 is applied at the D input at the first flip-flop. At the negative edge of the CLK pulse, this 1 is shifted into Q. The O of Q is shifted into R, O of R is shifted into S and O of S is shifted into T. The output of flip-flop just after time A are QRST=1000.

Fig. 1.24: 4 Bit Serial In-Serial Out Shift Register

At time B: Another 1 is applied in the data input of the first flip-flop. So at the negative CLK edge, this 1 is shifted to Q. The 1 of Q is shifted in R.,O of R shifted in S, O of S is shifted into T. so, at the end of time B the output of all the flip-flops are QRST=1100.

At time C: A O(zero) is applied in the D input of the 1st first flip-flop. At the negative CLK edge, this O shifts to Q. The 1 of Q shifts into R.,1 of R shifts into S, 1 of R shifts into S, O of S shifts into T. Hence the output becomes QRST=0110.

At time D: 1 is applied to D input of the first flip-flop. So this 1 shifts into Q at the negative transmission of CLK. The previous O of Q shifts into R, the 1 of R shifts into S, the 1 of S shifts into T. Hence at the end of time D, the registers contains QRST=1011.

In the above steps, using 4 CLK pulses, we have shifted a 4 bit binary number 1011 in the register in a serial fashion.

To take out this binary number serially, we need another 4 CLK pulses and 4 O inputs into D pin of the first flip-flop. The binary

number leave the register serially through the T pin of the last flip-flop.

## 1.7.2 Serial In - Parallel Out (SIPO)

Fig. 1.25 : Bit Serial In - Parallel Out Shift Register

In this type of shifts register, data is entered serially into the register and once data entry completed it can be taken out parallelly. To take the data parallelly, it is simply required to have the output of each flip-flop to an output pin. All other constructional features are same as Serial In—Serial Out (SISO) register.

The shifting of data into SIPO is same as SISO registers. In the SIPO of Fig 1.25, a binary number, say 1011 would be shifted just like the manner as described in the previous section. It would take 4 CLK pulses to complete the shifting. As soon as shifting is completed, the stored binary number becomes available in the output pins QRST. SIPO register is useful to convert serial data into parallel data.

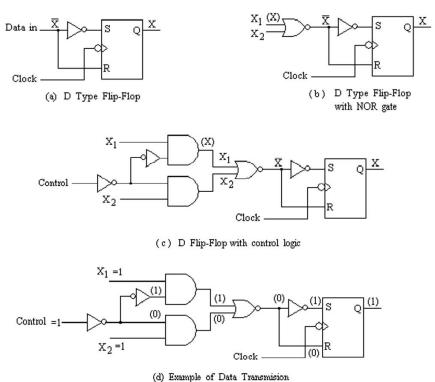

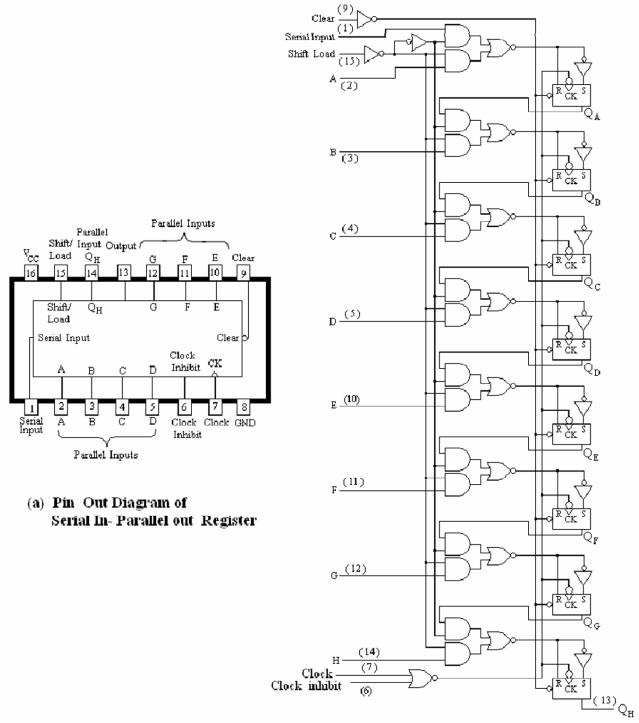

## 1.7.3 Palallel In-Serial Out (PISO)

PISO registers take data parallelly and shifts data serially. Commercially available TTL IC for PISO is 54/74166. To understand the functional block diagram of 54/74166 we should first understand the following Fig 1.26(a) is a clocked RS flipflop, which is converted to a D flip-flop by a NOT gate. The output of the flip-flop is 1 if Data IN ( $\overline{X}$ ) is 0. Next add a NOR gate as in Fig 1.26(b). Here, if  $X_2$  is at ground level,  $X_1$  will be inverted by the NOR gate. As for example, if  $X_1$  =1, then output of the NOR gate will be  $\overline{X}$  =0, thereby a 1 will be clocked into the flip-flop. This NOR gate allows entering data from two sources, either from  $X_1$  or  $X_2$ . To shift  $X_1$  into the flip-flop,  $X_2$  is kept at ground level and to shift  $X_2$  into the flip-flop,  $X_1$  is kept at ground level.

Fig. 1.26: Building Block of Parallel In-Serial Out Register

Now in Fig 1.26 (c) two AND gates and two NOT gates are added. These will allow the selection of data  $X_1$  or data  $X_2$ . If the control line is high, the upper AND gate is enabled and the lower AND gate is disabled. Thus, the data  $X_1$  will enter at the upper leg of the NOR gate and at the same time the lower leg of the

NOR gate is kept at ground. Opposite to this, if the control is low, the upper AND gate is disabled and the lower AND gate is enabled. So  $X_2$  will appear at the lower leg of the NOR gate and during this time the upper leg of the NOR leg gate is kept at ground level.

Fig 1.27 Circuit of 54/74166

(b) Logic Diagram of Serial In - Parallel Out Register If we study Fig 1.27 of PISO we see that circuit of Fig 1.26 (c) is repeated 8 times to form the 54/74/66 shift register. These 8 circuits are connected in such a style that it allows two operations: (1) The parallel data entry and (2) shifting of data serially through the flip-flop  $Q_A$  from  $Q_B$  toward

If Fig 1.27 the X<sub>2</sub> input of Fig 1.26( c ) is taken out from each flip-flop to form 8 inputs named as ABCDEFGH to enter 8 bit data parallelly to the register. The control is named here as SHIFT/LOAD which is kept low to load 8 bit data into the flip-flops with a single clock pulse parallelly. If the SHIFT/LOAD is kept high it will enable the upper AND gate for each flip-flop. If any input is given to this upper AND gate then a clock pulse will shift a data bit from one flip-flop to the next flip-flop. That means data will be shifted serially.

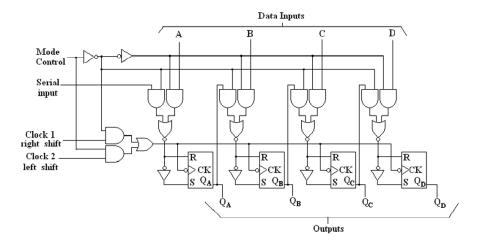

#### 1.7.4 Palallel In - Palallel Out Register (PIPO)

The register of Fig 1.27 can be converted to PIPO register simply by adding an output line from each flip-flop.

The 54/74198 is an 8 bits such PIPO and 54/7459A is a 4 bit PIPO register. Here the basic circuit is same as Fig 1.26(C). The parallel data outputs are simply taken out from the Q sides of each flip-flop. In Fig 1.28 the internal structure of 54/7459A is shown.

When the MODE CONTROL line is high, the data bits ABCD will be loaded into the register parallely at the negative clock pulse. At the same time the output is available  $Q_AQ_BQ_CQ_D$ . When the MODE CONTROL is low, then the left AND gate of the NOR gate is enabled. Under this situation, data can be entered to the register serially through SERIAL INPUT. In each negative transition, a data bit shifted serially from  $Q_A$  to  $Q_B$ , from  $Q_B$  to  $Q_C$  and so on. This operation is called right-shift operation.

With a little modification of the connection, the same circuit can be used for shift-left operation. To operate in shift-left mode, the input data is to be entered through D input pin. It is also necessary to connect  $Q_D$  to C,  $Q_C$  to B,  $Q_B$  to A as shown in Fig 1.28. MODE CONTROL line is high to enter data through the D input pin and each stored data bits of flip-flops will be shifted to left flip-flop on each negative clock transition. This is serial data and left shift operation.

To clock inputs—clock1 and clock2 is used here to perform shift right and shift left operation..

Hence 54/7495A can be used as Parallel In – Parallel Out shift register as well as shift right and shift left register.

Fig. 1.28: Parallel In - Parallel Out Shift Register

#### **CHECK YOUR PROGRESS 6**

- 15. Shift registers are

- (a) basically a synchronous circuit

- (b) an asynchronous circuit

- (c) permanent memory

- (d) none of these

- 16. In SIPO

- (a) data enters parallely and leaves serially

- (b) data enters serially and leaves serially

- (c) data enters serially and leaves parallely

- (d) data enters parallely and leaves parallely

#### 1.8 LET US SUM UP

- Digital circuits are of two categories combinational and sequential

- A combinational circuit is some combinations of logic gates as per specific relationship between inputs and outputs.

- Adder and subtractor circuits can perform binary addition and subtraction.

- A multiplexer is a combinational circuit which selects one of many inputs.

- Demultiplexer is opposite to a multiplexer.

- An encoder generates a binary code for input variables.

- A decoder decodes an information receives from n input lines and transmits the decoded information to maximum outputs.

- A sequential circuit's output depends on past output and present inputs.

- A flip-flop is basically a single cell of memory which can store either 1 or 0.

- Sequential circuits use flip-flop as their building block.

- There are many types of flip-flop viz RS, D, JK, MS flip-flop.

- A counter is a sequential circuit that can count square waves give as clock input. There are two types of countersasynchronous and synchronous counter.

- Shift registers are also sequential circuit which are used to store binary bits. They are of four different types -Serial In- Serial Out, Serial In- Parallel Out, Parallel In- Parallel Out and Parallel In-Serial Out register.

# 1.9 ANSWERS TO CHECK YOUR PROGRESS

- 1. (b) 2. (c) 3. (a) 4. (b)

- 5. (c) 6. (d) 7. (b)

- 8. (a) 9. (b) 10. (b)

- 11. (c) 12. (b) 13. (c)

- 14. (a) False (b) False (c) True (d) True

- 15. (a) 16 (c)

#### 1.10 FURTHER READINGS

- 1. Mano, M. M., Digital Logic and Computer Design, PHI.

- 2. Mano, M. M., Computer System Architecture, PHI.

- 3. Malvino, Albert Paul & Leach, Donald P., Digital Principles and Applications, Mcgraw-Hill International.

- 4. Lee, Samual C, Digital Circuits and Logic Design, PHI.

- 5. Talukdar, Dr. Pranhari, Digital Techniques, N. L. Publications.

## 1.11 MODEL QUESTIONS

- 1. Distinguish between combinational circuit and sequential circuit.

- With truth table and logic diagram explain the working of a fulladder circuit.

- With truth table and logic diagram explain the working of a Full-subtractor circuit.

- 4. What do you mean by multiplexer? With diagram explain the working of a 8-to-1 multiplexer.

- 5. Explain the principle of an encoder. Draw a decimal-to-BCD encoder.

- 6. What are the differences between asynchronous and synchronous counter? Draw a MODE-8 counter and explain its working principle.

- 7. Draw a logic diagram with output wave form of a 4-bit Serial In- Parallel Out shift register for an input of 1101. Explain its operation.

- 8. Why is square wave clock pulse converted to a narrow spike to be used for flip-flops? Draw a RC differentiator circuit to convert a square wave into a narrow spike.

- 9. What is called racing? To get rid of racing what techniques are used?

- What do you mean by magnitude comparator? Draw a block diagram and the function table of the magnitude comparator SN 7485.

\*\*\*\*\*

#### **UNIT STRUCTURE**

- 2.1 Learning Objectives

- 2.2 Introduction

- 2.3 Input-Output Devices

- 2.4 Input-Output Interface

- 2.5 Different I/O techniques

- 2.5.1 Programmed I/O

- 2.5.2 Interrupt-Driven I/O

- 2.5.3 Direct Memory Access (DMA)

- 2.5.4 I/O Processors

- 2.6 Let Us Sum Up

- 2.7 Further Readings

- 2.8 Answers To Check Your Progress

- 2.9 Model Questions

#### 2.1 LEARNING OBJECTIVES

After going through this unit, you will be able to:

- learn about the input and output devices

- learn how data transfer takes place between computer and peripherals

- know about the interrupts

- describe input-output processors

#### 2.2 INTRODUCTION

In the previous unit, we have learnt about the various digital components. In this unit, we will discuss how the data is fed to the computer and the way they are being processed, that is, how the data is being transferred to and from the external devices to the CPU and the memory.

#### 2.3 INPUT- OUTPUT DEVICES

The computer communicates with the users with the help of input and output devices. Input devices enter data and instructions into the

computer for processing and the output devices display the result obtained for the users to see. The input-output devices attached to the computer are also known as peripherals. There are three types of peripherals: input, output and input-output peripherals. Most common peripherals are:

- Keyboard,

- Monitor,

- Printers,

- The auxiliary storage devices such as magnetic disks and tapes.

A brief description of their functions are given below:

#### **Keyboard and Monitor:**

Keyboard allows the user to enter alphanumeric information. On pressing a key, a binary coded character, typically 7 or 8 bits in length is sent to the computer. The most commonly used code is a 7-bit code referred to as ASCII (American Standard Code For Information Interchange). Each character in this code is represented by a unique 7-bit binary code; thus a total of 128 different characters can be represented as shown in table 2.1

<u>Table 2.1</u> The American Standard Code for Information Interchange(ASCII)

|      | 0<br>0<br>0 | 0<br>0<br>1     | 0<br>1<br>0 | 0<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>1 | 1<br>1<br>0 | 1 1 1 |

|------|-------------|-----------------|-------------|-------------|-------------|-------------|-------------|-------|

| 0000 | NUL         | DLE             | SP          | 0           | @           | Р           |             | р     |

| 0001 | SOH         | DC <sub>1</sub> | !           | 1           | А           | Q           | а           | q     |

| 0010 | STX         | DC <sub>2</sub> | "           | 2           | В           | R           | b           | r     |

| 0011 | ETX         | DC <sub>3</sub> | #           | 3           | С           | S           | С           | S     |

| 0100 | EOT         | DC <sub>4</sub> | \$          | 4           | D           | Т           | d           | t     |

| 0101 | ENQ         | NAK             | %           | 5           | Е           | U           | е           | u     |

| 0110 | ACK         | SYN             | &           | 6           | F           | V           | f           | V     |

| 0111 | BEL         | ETB             | į           | 7           | G           | W           | g           | w     |

| 1000 | BS          | CAN             | (           | 8           | Н           | X           | h           | x     |

| 1001 | НТ          | ЕМ              | )           | 9           | I           | Υ           | i           | у     |

| 1010 | LF          | SUB             | *           | •           | J           | Z           | j           | Z     |

| 1011 | VT          | ESC             | +           | •           | К           | [           | k           | {     |

| 1100 | FF          | FS              | ,           | <           | L           | 1           | 1 .         | 1     |

| 1101 | CR          | GS              | -           | =           | М           | ]           | m           | }     |

| 1110 | so          | RS              | •           | >           | N           | ٨           | n           | 2     |

| 1111 | SI          | US              | 1           | ?           | О           | -           | 0           | DEL   |

The Control Character are:

NUL - Null

SOH - Start of Heading

STX - Start of Text

ETX - End of Text

EOT - End of Transmission

ENQ - Enquiry

ACK - Acknowledge

BEL - Bell

BS - Backspace

HT - Horizontal Tab

LF - Line feed

VT - Vertical Tab

FF - Form feed

CR - Carriage Return

SO - Shift Out

SI - Shift In

DLE - Data Line Escape

DC1, DC2, DC3, DC4 - Device Controls

NAK - Negative Acknowledge

SYN - Synchronous Idle

ETB - End of Transmission Block

CAN - Cancel

EM - End of Medium

SUB - Substitute

ESC - Escape

FS - File Separator

GS - Group Separator

RS - Record Separator

US - Unit Separator

DEL - Delete

Video monitors may be of different types but most commonly used one is the CRT (Cathode Ray Tube) monitors. Another one that becomes popular now-a-days is LCD (Liquid Crystal Display) monitor.

The monitor displays a cursor on the screen which marks the position on the screen where the next character is to be inserted.

#### Printers:

Printers produce a hard copy of the output data. Based on the technology used printers may be either impact or non-impact. Impact printers operates by using a hammer to strike a character against an inked ribbon; the impact then causes an image of the character to be printed. Types of impact printers are dot-matrix, daisy wheel, line printers. Non-impact printers do not touch the paper while printing. Non-impact printers like Laser printers uses a rotating photographic drum to imprint the character images and then transfer the pattern onto the paper. Inkjet, deskjet and thermal printers also fall under this category.

#### Magnetic Tapes and Disks:

The magnetic tape drives and disk drives are used to read and write data to and from the magnetic tapes and the disks. The surfaces of these output devices are coated with magnetic material so as to store data in them. These surfaces can be magnetized and the presence of a magnetic field represents a '1' bit and the absence of a magnetic field represents a '0' bit. The magnetic disk is a circular metal disk that is coated on both sides to store data. The magnetic tape stores data

in a sequential manner. To process a data in a tape ,it must begin searching at the beginning and check each record until the desired record is found.

In case of magnetic disks, the data can be stored and accessed directly and so it is fast. Floppy disks, hard disks are examples of magnetic disks.

|     |   |   | / |  |

|-----|---|---|---|--|

| E N |   | _ | Ŧ |  |

|     | N |   |   |  |

|     |   |   |   |  |

#### **CHECK YOUR PROGRESS**

| 1. | Fill | in | the | blanks | : |

|----|------|----|-----|--------|---|

|----|------|----|-----|--------|---|

- (a) The Keyboard is a \_\_\_\_\_device.

- (b) Daisy Wheel is a \_\_\_\_\_ printer and the Deskjet is a \_\_\_\_\_ printer.

- (c) Phosphor on being struck by \_\_\_\_\_ emits light on the monitor screen.

- (d) Magnetic tape stores data on its \_\_\_\_\_ sides.

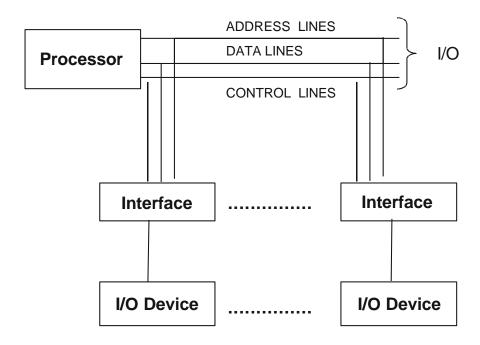

#### 2.4 I/O INTERFACE

The I/O Interface is responsible for exchange of data between the peripherals and internal storage of the computer. Instead of directly connecting the peripherals to the system bus, an I/O Interface is used in between because,

- The mode of operation of the different peripherals is different from the operation of the CPU and memory.

- The data transfer rate of the peripherals is much slower compared to that of CPU and memory.

- 3. Peripherals use different data formats than the word format in the CPU and memory.

The interface units are hardware components between the CPU and the peripherals that supervise and synchronize all the I/O transfers.

Two main types of interfaces are CPU Interface that corresponds to the system bus and input-output interface that is tailored to the nature and operation of the peripheral devices. The major functions of the I/O Interface units are :

- 1. Data Conversion; conversion between digital and analog signals.

- 2. Synchronization; synchronizes speeds of the CPU and other peripherals.

- Device Selection; selection of the I/O device by the CPU in a queue manner.

Input-Output devices are attached to the processor with the help of the I/O Interface as shown in the figure below:

Fig. 2.1: Processor and the I/O Interface

The I/O interface circuit also has an address decoder, control circuits and data and status registers. Whenever the CPU has to communicate with a particular device, it places its address in the address lines; the address decoder in the address lines then helps in recognizing the address of its connected I/O device. The I/O interface can also generate addresses associated with the device that it controls. The control circuits accept the detailed control information from the CPU. The I/O interface also holds the responsibility of data buffering. The data registers in it

holds the data being transferred to and from the interface. This is necessary as the data transfer rate into and out of the CPU or memory is quite high as compared to the peripheral devices. The status registers provides the current status information relevant to the input-output device operation. The data and status registers are connected to the data bus.

The input-output interface can detect errors and then after detection reports them to the CPU.

#### **CHECK YOUR PROGRESS**

- 2. Write True or False:

- (a) The I/O Interface is a hardware component in the computer.

- (b) The Control lines of the System Bus carries the addresses of the peripherals.

- (c) Main memory can transfer data at high speed compared to the peripherals.

- (d) The Status register in the I/O Interface holds the data that is being transferred.

#### 2.5 DIFFERENT I/O TECHNIQUES

There are different I/O techniques in the computer. Some may involve the CPU for transferring data between the computer and the input-output devices and others may directly transfer data from and to the memory units. The three possible techniques for I/O operations are:

- Programmed I/O,

- Interrupt Driven I/O,

- Direct Memory Transfer (DMA)

#### 2.5.1 Programmed I/O

In the Programmed I/O, data transfer takes place between the peripherals and the processor during program execution.

When the CPU encounters an I/O instruction, while executing a computer program, it immediately sends the address of the particular I/O device in the address lines of the I/O bus and also at the same time it issues a command to the particular I/O interface in the control lines of the I/O bus.

There are four types of commands that an interface may receive:

- o Control command

- Status command

- o Read command

- o Write command

A *Control command* is used to activate the peripheral and tell it what to do. This command depends on the type of the particular peripheral.

A *Status command* is used to test the various status of the peripheral and the I/O interface.

A *Read command* causes the interface to get the data from the peripheral and place it in its data registers. The interface then places the data in the data lines of the bus for the processor when it requests for it.

A Write command causes the interface to transfer the data from the bus into its data registers. When it completes transferring data to its data registers, it then transmits that data to the particular I/O device.

In Programmed I/O, the CPU must constantly check the status of the I/O interface. That is, on issuing a command to the I/O interface, the processor must wait until the I/O operation is complete. This is a time consuming process as it keeps the CPU needlessly busy.

#### 2.5.2 Interrupt- Driven I/O

In Programmed I/O the processor has to constantly monitor the status of the interface to check when it is ready for data transfer. This causes wastage of the CPU time. An alternative to this method is the Interrupt-Driven method, where after issuing a command to the interface, the CPU can switch to execution of other programs in the computer. When the interface is ready for the transfer, it will immediately send an interrupt signal to the CPU. The CPU will then do the data transfer and resume back to what it was doing before it received the interrupt signal. One of the bus control lines, called an Interrupt Request Line, is dedicated for this purpose.

In this method, the advantage is that the CPU need not spend time waiting for an I/O operation to be completed, thereby increasing its efficiency.

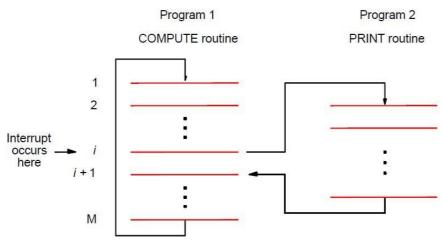

The routine that is executed when there is an interrupt request is called Interrupt Service Routine (ISR). When the CPU gets an interrupt signal, while it is executing an instruction of a program, say instruction I, it first finishes execution of that instruction. It then stores the current contents of the Program Counter (PC), which now points to the next instruction i+1, and stores it in a memory stack. This is its return address after execution of the ISR. The control then branches to the service routine that processes the required I/O transfer.

#### Determining the I/O device requesting Interrupt

When the CPU receives an interrupt signal over the interrupt request line, it must determine which I/O interface has sent it. There are different techniques for determining this. They are:

- 1. Software Poll

- 2. Vectored Interrupt

- 3. Bus arbitration

#### 1. Software Poll

When the CPU detects an interrupt, it branches to an interrupt-handler. This interrupt-handler poll each I/O interface to determine which interface caused the interrupt. The interface which signaled the interrupt responds positively to it. This is time-consuming.

#### 2. Vectored Interrupt

This is a more efficient technique which uses a daisy chain. It provides a hardware poll. The interrupts are signaled through a common Interrupt request line. The interrupt acknowledge line is daisy-chained through the I/O interface. On receiving an interrupt, CPU sends an acknowledge signal through it. The interface which sent the interrupt responds by placing its vector on the data lines.

#### 3. Bus Arbitration

At a time only one interface can send an interrupt signal. When the CPU detects the interrupt signal, it acknowledges through the interrupt acknowledge line. The interface signaling the interrupt then places its vector on the data lines.

#### **Handling Multiple Interrupts**

There may be multiple interrupts simultaneously. In those cases the CPU has to decide which one to service first. Priorities are thus assigned to the I/O interfaces to determine the order in which the interrupts are serviced. The devices having higher speeds such as the disks are given higher priorities, while the slower devices such as keyboards are given low priority. Also higher priority is given to the interrupts which if delayed may cause serious consequences. So, when two device interfaces sends interrupt requests to the processor at the same time, the device having higher priority will be serviced first.

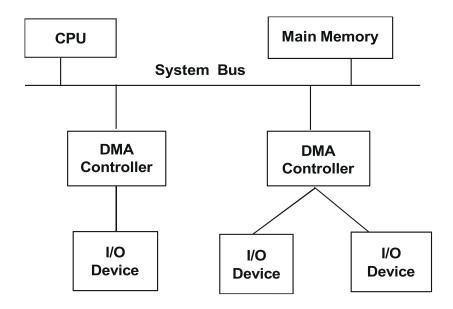

#### 2.5.3 Direct Memory Access

When large blocks of data are to be transferred between memory and high-speed I/O devices, a more efficient approach is used. This alternative technique is the Direct Memory Access (DMA) technique. It eliminates the continuous intervention of the CPU in transferring data.

DMA transfers are performed by a DMA controller, which is a control unit in the I/O interface. This unit carries out the functions of the processor when accessing the main memory during the data transfers. In DMA transfers, the controller takes control of the memory buses from the CPU and does the transfer between the peripheral and the memory.

Fig. 2.2 : DMA Controllers in a Computer System

When the CPU gets an instruction that involves huge amount of data transfer while executing a computer program, it issues a command to the DMA Controller sending the address of the I/O device, the number of words to be transferred and whether a read/write operation is to be performed. Thus the DMA, CPU just initializes the data transfer and become free for other works. i.e.,

the data transfer operation is completed by the DMA controller without the continuous involvement of the CPU.

The transfer may be in two ways / modes:

**Burst Transfer**: By Burst Transfer a block of words is transferred in a continuous burst. This mode is needed for fast devices where data cannot be stopped until the entire block is transferred. Then the controller informs the CPU by sending an interrupt signal.

**Cycle Stealing:** The controller transfers one word at a time and return the bus control to the CPU. The CPU then temporarily suspends its operation for one memory cycle to allow the DMA transfer to steal its memory cycle.

The DMA controller uses a register for storing the starting address of the word to be transferred, a register for storing the word count of the transfer and another register contains the status and the control flags. The status and the control registers are shown below

| IRQ | ΙE |  | R/W | Done |

|-----|----|--|-----|------|

|-----|----|--|-----|------|

IRQ: Interrupt Request

IE : Interrupt Enabled

R/W: Read or Write operation

The IRQ bit is set to 1 when the controller has requested an interrupt. When the data transfer is completed, it sets the IE to 1 thereby to raise an interrupt. When it is ready for the next command, after completion, the Done bit is set to 1. When the R/W bit is 1, the controller performs a Read operation, otherwise a Write operation is performed.

Whenever a word is transferred, the DMA Controller increments its address register to point to the next word to be transferred

and decrements its word count register. When finally the word count becomes zero, the controller stops any further transfer and informs the CPU by raising an interrupt.

#### **CHECK YOUR PROGRESS**

#### 3. Write True or False:

- (a) There are only 2 techniques for the I/O operations in the computer.

- (b) Read command in Programmed I/O causes the interface to get the data from I/O devices and place it in its data registers.

- (c) Interrupt Driven I/O wastes the CPU time needlessly.

- (d) Interrupt Service Routine is an interrupt signal.

- (e) In Direct Memory Access, the data transfer takes place directly between the peripheral and the memory.

- (f) The DMA Controller carries out the functions of the processor when accessing the main memory during the data transfers.

#### 2.5.4 I/O PROCESSOR

An Input – Output processor (IOP) is a processor in addition to the CPU. It directly communicates with the input and output devices. The IOP need not interfere with the tasks of the CPU as they themselves can fetch and execute the instructions. Other than fetching and executing I/O instructions the Input Output processor can also do processing tasks like arithmetic, logic and branching.

Data from the devices are first collected into the IOP and then transferred to the memory directly by stealing one memory cycle from the CPU. Similarly data is transferred from memory to IOP first and the the gathered data is sent to the respective I/O devices.

#### 2.6 LET US SUM UP

- Data transfer between the peripherals and the computer takes place through an Input-Output Interface.

- Each input/output device is connected to the system bus with the help of the I/O interface.

- There are three different I/O techniques :

- 1) Programmed I/O

- 2) Interrupt-Driven I/O

- 3) Direct Memory Access (DMA)

- In Programmed I/O, the processor must constantly check the status of the interface until the I/O task is completed, which is a wastage of the CPU time.

- In Interrupt-driven I/O, the processor is free to perform other tasks while the I/O operation is going on. On its completion, the interface sends an interrupt signal to the CPU.

- In DMA, data is transferred directly between the memory and the external devices without intervening the CPU.

## 2.7 FURTHER READINGS

- M. Morris Mano, Computer System Architecture, PEARSON Prentice Hall.

- 2. Hamacher, Vranesic, Zaky Computer Organization, Mc Graw Hill.

- 1. a) Input

- b ) Impact, Non-impact

- c) electrons

- 2. a) True

- b) False

- c ) True

- d) False

- 3. a) False

- b) True

- c ) False

- d ) False

- e) True

- f) True

## 2.9 MODEL QUESTIONS

- 1. Briefly describe the work of the I/O Interface in data transferring.

- 2. Describe the functions of the I/O Interface units in a computer.

- 3. What is the difference between Programmed I/O and Interrupt Driven I/O? What are their advantages and disadvantages?

- 4. What is the task of the DMA Controller when there is a request for memory transfer?

- 5. What are the methods for determining which I/O device has requested an interrupt?

- 6. Why are priorities being assigned to the external devices?

\*\*\*\*

## **UNIT-3** MEMORY UNIT

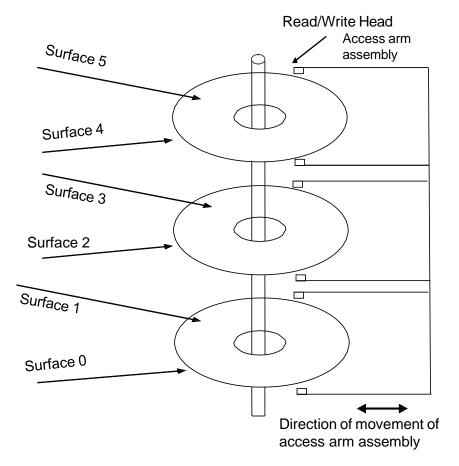

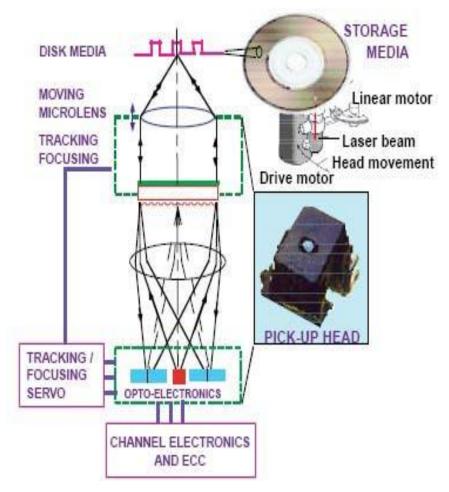

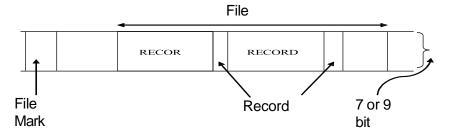

#### **UNIT STRUCTURE** 3.1 Learning Objectives 3.2 Introduction 3.3 Memory Hierarchy 3.4 Main Memory 3.5 Semiconductor RAM 3.5.1 Static and Dynamic RAM 3.5.2 Internal Organization of Memory Chips **ROM** 3.6 3.6.1 Types of ROM 3.7 Locality of Reference 3.8 Cache Memory 3.8.1 Cache Operation - an overview 3.9 Mapping Functions 3.9.1 Direct Mapping 3.9.2 Associative Mapping 3.9.3 Set-Associative Mapping 3.10 Replacement Algorithm 3.11 Virtual Memory 3.11.1 Paging 3.12 Magnetic Disk 3.12.1 Data Organization in Magnetic Disk 3.12.2 Disk Access Time 3.13 **RAID** 3.14 **Optical Memory** 3.14.1 CD-ROM 3.14.2 DVD Disks 3.15 Magnetic Tape 3.16 Let Us Sum Up 3.17 Further Readings 3.18 Answers To Check Your Progress

**Model Questions**

3.19

#### 3.1 LEARNING OBJECTIVES

After going through this unit, you will be able to:

- learn about main memory

- describe the role of RAM, ROM and their types

- · learn the concept of locality of reference

- learn about cache and virtual memory

- describe different types of mapping techniques

- · decribe the mechanism of paging

- illustrate the organization of data in magnetic disks as well as magnetic tapes

- learn about RAID technology

- · describe the technology of optical memory

#### 3.2 INTRODUCTION

In the previous unit, we have learnt about the peripheral devices associated with a computer system and various techniques with the help of which data transfers between the main memory and the input-output devices takes place.

In this unit we shall discuss about various types of memory associated with a computer system including main memory, cache and virtual memory and various technology associated with these memory units. Finally, we conclude the unit discussing the concept of secondary memory along with their types.

#### 3.3 MEMORY HIERARCHY

The computer stores the programs and the data in its memory unit. The CPU fetches the instructions out of the memory unit to execute and process them.

Memory can be primary (or main) memory and secondary (or auxiliary) memory. Main memory stores programs and data currently executed by the CPU of a computer. Auxiliary memory provides backup storage of information. Data as well as instructions are transferred from the secondary memory to the main memory whenever it is needed by the CPU.

The capacity of the memory is typically expressed in terms of bytes or words (1 byte = 8 bits). Word lengths are commonly 8 bits, 16 bits and 32 bits. The size of a word is generally the number of bits that are transferred at a time between the main memory and the CPU.

Memory has different locations, which are called its addresses, to store the data. There are different methods for accessing those address locations such as **sequential access**, direct access and **random access**.

- In Sequential access method, the records or the data are accessed in a linear fashion, from its current location in the memory to the desired location moving through each and every record in the memory unit. For example, in case of the magnetic tapes this method is used.

- In *Direct Access*, each record has different addresses based on the physical location of the memory and the shared Read/ Write head moves directly to the desired record. This method is used in magnetic disks.

- In Random access each location can be randomly selected and accessed directly. Main memory can be randomly accessed.

Memory has two basic operations: *Read* and *Write* operations. In Read operation, the processor reads data from a particular memory location and transmits that data to the requesting device via bus. On the other hand, a memory Write operation causes the memory to accept data from a bus and to write that particular information in a memory location.

Regarding the speed of the memory, there are two useful measures of the speed of memory units: *Memory Access Time* and *Memory Cycle Time*.

Memory Access Time is the time between the initiation of a memory operation and the completion of that operation. Memory Cycle Time is the minimum time delay that is required between the initiation of two successive memory operations, for example between two successive memory read operations.

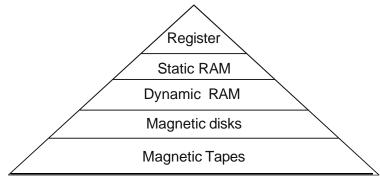

The computer system has a memory hierarchy consisting of the storage devices in it. A typical memory hierarchy is illustrated in the

Fig. 3.1: Memory Hierarchy

There are three key characteristics of the memory. They are *cost*, *capacity* and *access time*. On moving down the memory hierarchy, it is found that the cost of the storage devices decreases but their storage capacity as well as the memory access time increases. In other words, the smaller memories are more expensive and much faster. These are supplemented by the larger, cheaper and slower storage devices.

Thus from the above figure it can be seen that the registers are at the top of the hierarchy and so provides the fastest, the smallest and the most expensive type of memory device for the CPU to access data. Registers are actually small amount of storage available on the CPU and their contents can be accessed more quickly than any other available storage. They may be 8-bit registers or 32-bit registers according to the number of bits that they can hold in them.

Magnetic disks and Magnetic Tapes are the secondary storage mediums whose data holding capacities are much larger than the Processor Registers and the semiconductor memories which cannot hold all the data to be stored in the computer system. The magnetic tapes are more suited for the off-line storage of the large amounts of the computer data. The data are kept as records which are again separated by gaps.

#### 3.4 MAIN MEMORY

The main memory is the central storage unit of the computer system. Main memory refers to the physical memory which is internal to a computer. The word "Memory" when used usually refers to the Main Memory of the computer system. The computer can process only

those data which are inside the main memory. For execution, the programs and the data must be first brought into the main memory from the storage device where they are stored. Computer memory has a crucial role in the performance, reliability and the stability of the system. It is also an important factor in the software support of the system. More number of software can be used with more memory than with lesser ones. There are two types of main memory:

- RAM (Random Access Memory) and

- ROM (Read Only Memory).

**RAM**: In RAM, it is possible to both read and write data from and to the memory in a fixed amount of time independent of the memory location or address. RAM is also a volatile memory which means it stores the data in it as long as power is switched on. Once the power goes off, all the data stored in it is also lost. Therefore, a RAM cell must be provided a constant power supply.

**ROM**: ROM is a non-volatile semiconductor memory; that is, it doesn't lose its contents even when the power is switched off. ROM is not re-writable once it has been written or manufactured. ROM is used for programs such as bootstrap program that starts a computer and load its operating system.

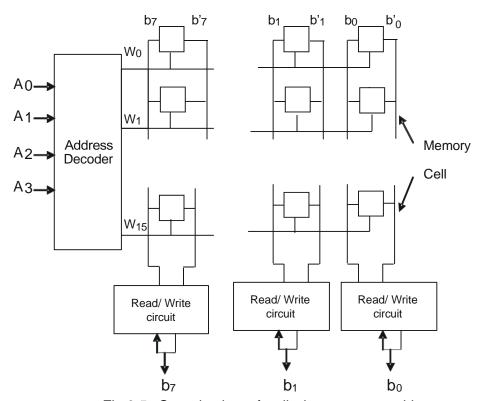

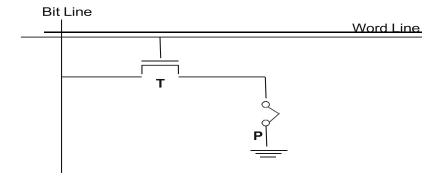

#### 3.5 SEMICONDUCTOR RAM

The basic building block of the semiconductor memories is the RAM chip. RAM is actually made up of a number of RAM chips. They contain a number of memory cells, which are electronic circuits having two stable states: 0 and 1. The binary information are stored in the form of arrays having rows and columns in the memories. With the advent and advances of VLSI (Very Large Scale Integration) circuits, thousands of memory cells can be placed in one chip. As a result, the cost of the semiconductor memories has dropped dramatically.

#### 3.5.1 Static and Dynamic RAM

There are two main types of semiconductor RAM Memories: Static RAM (SRAM) and Dynamic RAM (DRAM) and also their

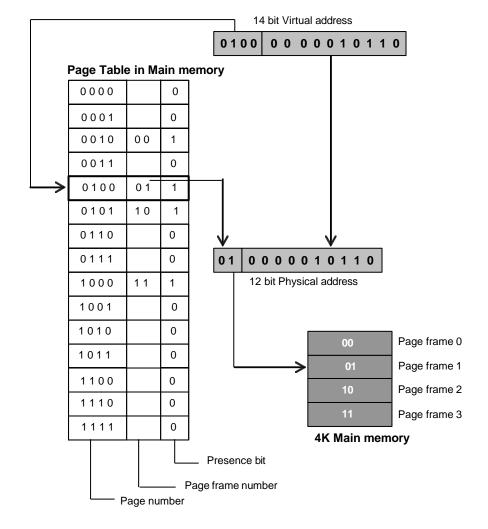

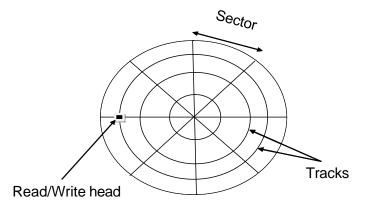

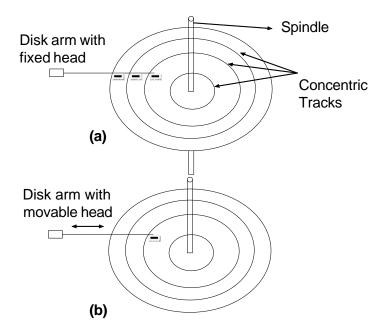

variations.